في جملة واحدة

أتمّت منظومة الذكاء الاصطناعي (AI) المدفوعة بالفيزياء من Quilter أتمتة معظم تخطيط لوحات الدوائر المطبوعة (PCB) لحاسوب معقّد يعمل بنظام لينكس، ما أتاح إقلاعًا ناجحًا من المحاولة الأولى وفي جزء ضئيل من الزمن المعتاد. إذا أمكن توسيع النطاق، قد تتسارع وتيرة تطوير العتاد جذريًا، حتى لو ظلّت التصاميم فائقة التعقيد وعالية التردد هدفًا مستقبليًا.

التفاصيل

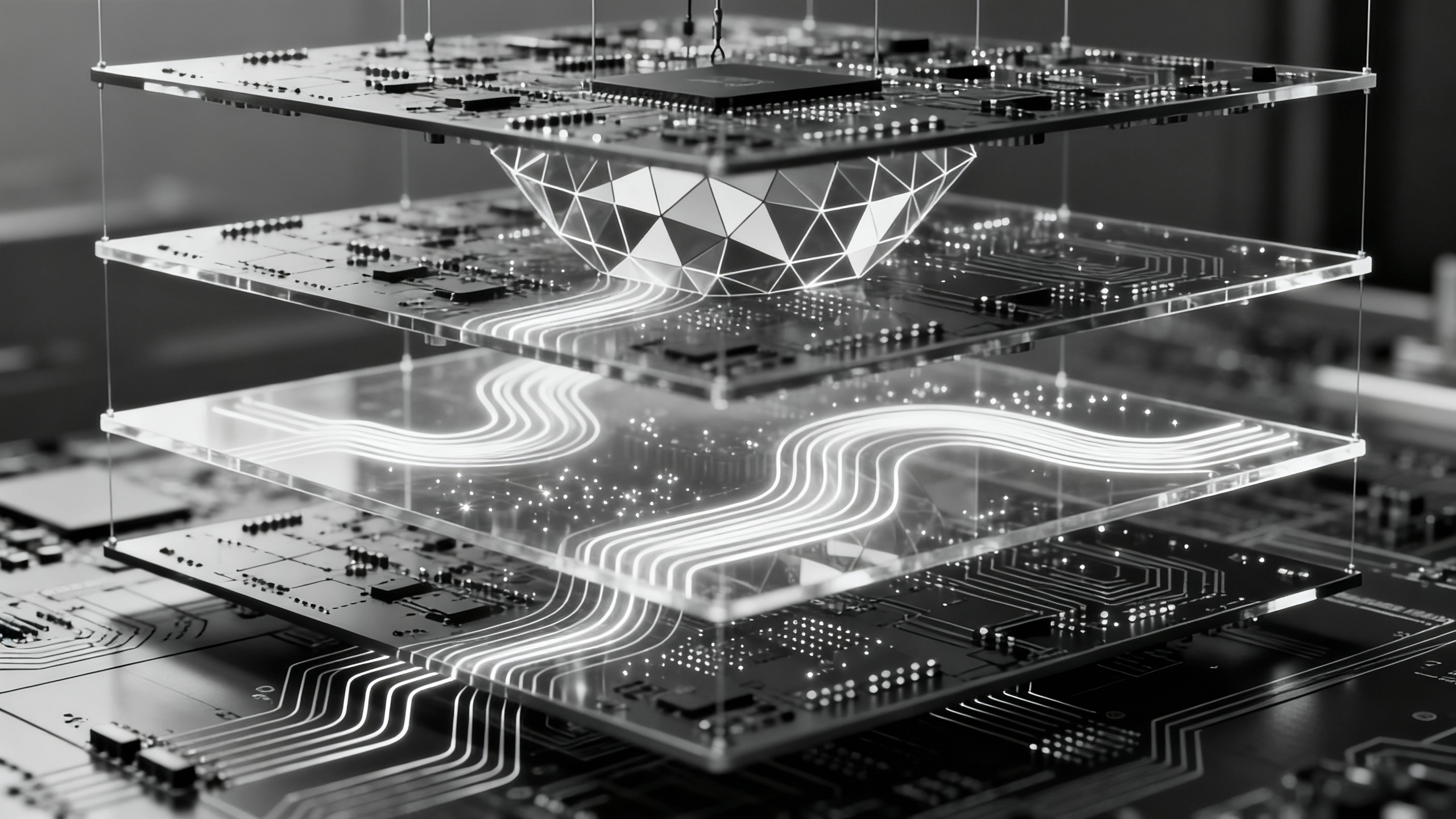

تقول شركة Quilter الناشئة في لوس أنجلوس إن نظام ذكائها الاصطناعي (AI) صمّم وساعد على تسليم حاسوب يعمل بنظام لينكس مكوّنًا من لوحتين ويعمل بكامل طاقته خلال أسبوع واحد — وهو إنجاز يستغرق عادةً قرابة ثلاثة أشهر. النظام، القائم على NXP i.MX 8M Mini، يضم 843 مكوّنًا و5,141 طرفًا (pins) عبر ثماني طبقات PCB مع مسارات بعرض 2 ميل (mil)، وقد أقلع ديبيان لينكس (Debian Linux) من المحاولة الأولى. تؤكد Quilter تحقيق تغطية توجيه (routing) بلغت 98% من دون أي انتهاكات لقواعد التصميم (DRC)، ما خفّض العمل البشري الفعلي إلى 38.5 ساعة بدلًا من 428 ساعة يقدّرها مصممو لوحات الدوائر المطبوعة (PCB) المحترفون. توني فاضل، المخضرم وراء iPod وiPhone، دعم الشركة ويعمل الآن مستشارًا لها.

على عكس النماذج اللغوية (LLMs)، يتعلّم نهج Quilter من خلال التفاعل مع الفيزياء — فيحسّن التموضع والتوجيه (routing) تحت قيود كهرومغناطيسية وحرارية وتصنيعية، من دون التدريب على أمثلة بشرية لتصاميم PCB. يمكن للمهندسين التحكّم في القيود، ومراجعة مخططات (layout) التي ينتجها الذكاء الاصطناعي، وإجراء الصقل النهائي. حاليًا يستهدف النظام تصاميم تصل إلى نحو 10,000 طرف (pins) وبترددات حتى قرابة 10 جيجاهرتز (GHz)، ما يجعله مناسبًا للغاية للوحات التقييم والاختبار والتحقق (validation). تعتمد Quilter تسعيرًا على أساس عدد الأطراف (pin count) — على غرار خدمات التخطيط (layout) البشرية — لكنها تعد بزمن تسليم أسرع بنحو 10 مرات، وهو تغيير قد يمكّن فرق العتاد من التكرار بوتيرة أعلى بكثير، حتى لو ظلّت التصاميم الأكثر تقدمًا وعالية التردد خارج النطاق في الوقت الراهن.

النقاط الرئيسية

- حاسوب يعمل بنظام لينكس صمّمه ذكاء اصطناعي (AI) مؤلف من لوحتين ومبني على NXP i.MX 8M Mini؛ يضم 843 مكوّنًا و5,141 طرفًا، وأقلع من المحاولة الأولى؛ ثماني طبقات PCB مع مسارات بعرض 2 ميل (mil).

- قلّص جهد التخطيط (layout) من 428 ساعة إلى 38.5 ساعة وقلّص الجدول الزمني من نحو 11 أسبوعًا إلى أسبوع واحد؛ حقق توجيهًا (routing) بنسبة 98% من دون انتهاكات لقواعد التصميم (DRC).

- نهج Quilter يتدرّب عبر اتخاذ قرارات قائمة على الفيزياء (وليس على نماذج لغوية LLMs) ولا يعتمد على مجموعات بيانات بشرية لـPCB، ويهدف إلى تجاوز أساليب التخطيط البشرية.

- الحدود الحالية: نحو 10,000 طرف ونحو 10 جيجاهرتز (GHz)؛ الأنسب الآن للوحات الاختبار والتقييم والتحقق بدلًا من الأنظمة الأعلى تعقيدًا وعالية التردد.

- نموذج الأعمال يعتمد تسعيرًا مبنيًا على عدد الأطراف (pin count) مع تسليم أسرع بنحو 10 مرات؛ يحتفظ المهندسون بالتحكّم في القيود والصقل النهائي؛ توني فاضل مستثمر ومستشار.

المصادر: 1